Cadence presenta Cerebrus

l’intelligenza artificiale velocizza la progettazione dei chip

Uno strumento avanzato per velocizzare la progettazione, la produzione e l’arrivo sul mercato di chip di ogni genere.

Cadence, nota azienda specializzata nella progettazione, sviluppo e commercializzazione di soluzioni per il design di circuiti integrati, SoC e circuiti stampati, ha svelato Cerebrus.

Si tratta di uno strumento che utilizza il machine learning e che permetterà alle aziende di progettare nuovi chip in modo molto più veloce ed efficiente oltre che in tempi record.

Per anni, se non decenni, gli strumenti di progettazione di schede e chip sono stati in grado di automatizzare il posizionamento e la creazione di percorsi tra i vari strati coinvolti nella realizzazione del dispositivo.

Il problema è che tali strumenti richiedono la continua supervisione di un team di ingegneri per assicurarsi che tutto sia a posto e funzioni perfettamente. Cerebrus semplifica la procedura di convalida manuale e la riduce all’utilizzo di un’unica figura che è chiamata soltanto a convalidare il progetto finale.

Un approccio nuovo basato sull’intelligenza artificiale che assicura un enorme risparmio di tempo e costi per i progettisti di chip introducendo quindi benefici enormi in tanti aspetti della fase di progettazione.

Un chip subisce spesso delle modifiche nel processo di progettazione e anche nelle fasi di test e produzione al fine di ottimizzare le prestazioni, l’efficienza e l’area occupata (acronimo PPA, power, performance, area).

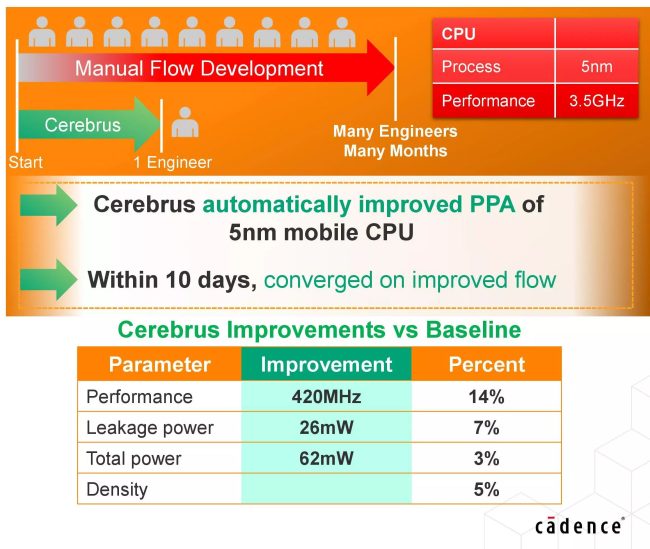

Cadence ha dimostrato che con un esempio di design a 5 nm Cerebrus permette di ottenere processori che lavorano a frequenze più elevate (+14%), sono contraddistinti da una densità di transistor maggiore (+5%) e correnti di dispersione minori (-7%).

I risultati presentati da Cadence sono stati ottenuti combinando il lavoro di Cerebrus con la supervisione di un ingegnere specializzato in soli 10 giorni contro i mesi di pianificazione e ottimizzazione da parte di una dozzina di ingegneri che collaborano servendosi degli attuali strumenti di progettazione di chip.

Fonte: ilsoftware.it